Breakout Board#

This device provides user-facing access for headstage, miniscope, and auxiliary data IO.

- Design Repository:

- Compatibility:

PCIe Controller, Headstage-64, Neuropixels-1.0f Headstage, Miniscopes, Neuropixels-1.0e Headstage, Neuropixels-2.0e Headstage, RHS2116 Headstage

Overview#

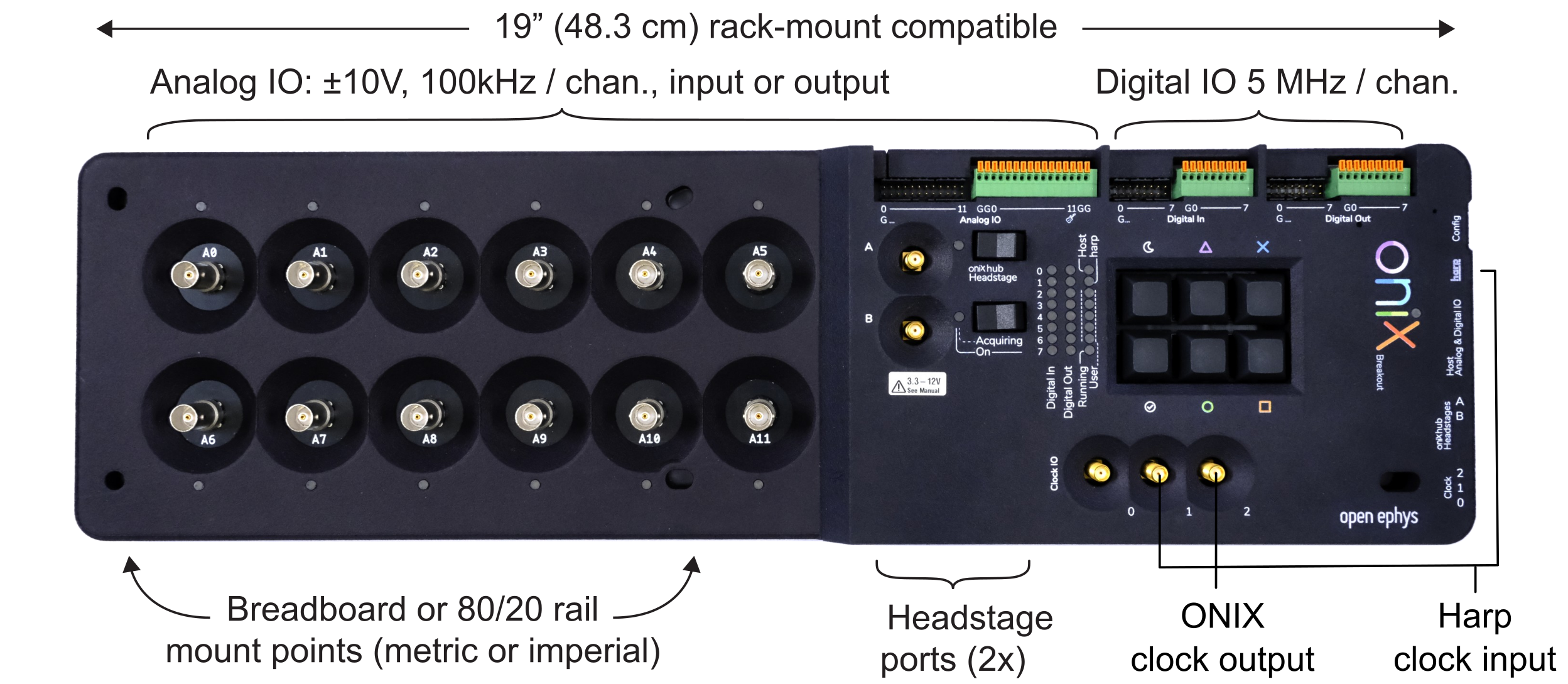

The ONIX Breakout Board allows bench access to the IO provided by the PCIe Controller.

ONIX Breakout Board v1.6.#

Features#

The Breakout Board provides access to the following IO:

2x headstage port feed-throughs, each with a power switch.

2x passive, high-speed clock feed-throughs. These can be used to connect to the clock input and clock output on the PCIe controller.

12x passive, ESD-protected, analog feed-throughs.

BNC, ribbon, or direct wire access to 12 analog inputs or outputs. These have a ±10V range and are sampled at 100 kHz.

Ribbon cable or direct, wire-access to 8 digital outputs and 8 digital inputs. These are 5V compliant and are sampled at 5 MHz.

HARP synchronization clock input bus

Additionally, it has the following features: